#### **HF Receivers, Part 3**

#### Introduction to frequency synthesis;

#### ancillary receiver functions

#### **Adam Farson**

#### VA7OJ

#### View an excellent tutorial on receivers

Another link to receiver principles

9 January 2005

NSARC HF Operators – HF Receivers 3

# **Basic Principles of Frequency Synthesis**

#### Phase-locked loop (PLL):

- Output of a voltage-controlled oscillator (VCO) is divided down to a low frequency and compared to a fixed reference frequency in a phase detector.

- Phase-detector output voltage (error signal) is zero when divideddown VCO output and reference are in phase. Any VCO ∆f causes + or – error signal, which pulls VCO back in phase with reference.

- Output frequency is set by varying division ratio of VCO divider.

- VCO and reference divider output freq. = tuning step (e.g. 100 Hz).

- Further reading.

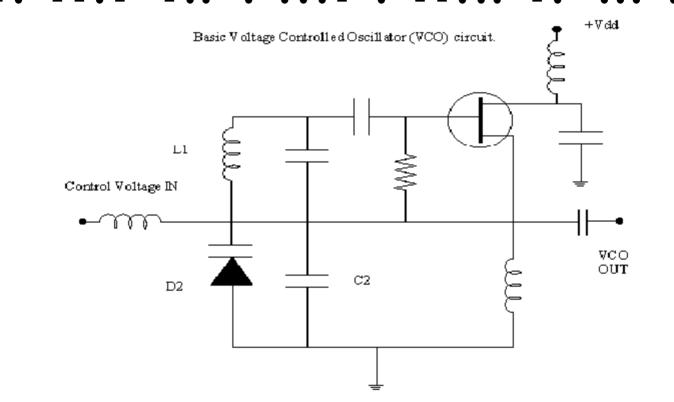

## Voltage-Controlled Oscillator (VCO)

- L1, C2 and D2 determine frequency of oscillation.

- D2 is a varactor (varicap).

- Increasing control voltage (error signal) decreases D2 capacitance, increasing frequency.

- 9 January 2005 NSARC HF Operators HF Receivers 3

# A Simple PLL Synthesizer

10 to 20 MHz (in 1 kHz steps) 10 MHz CRYSTAL 1 kHz 10 MHz 1 kHz Div. by n Div. by 10000 PHASE DIVIDER DIVIDER OSCILLATOR VCO DETECTOR n = 10000 to20000 Feedback Loop SIMPLIFIED PLL FREQUENCY SYNTHESIZER

- VCO output and 10 MHz reference are both divided down to 1 kHz, then compared in phase detector. Any phase difference causes error voltage on feedback loop. This "pulls" VCO back into exact phase with reference.

- "Divide-by-n" divider ratio determines output frequency (variable in 1 kHz steps).

NSARC HF Operators – HF Receivers 3

### Synthesizer Design Criteria

- Resolution (step size): determined by VCO operating frequency and division ratio. 100 or 10 Hz in earlier designs, 1 Hz in current radios.

- Trade-off: in classical PLL designs, smaller step size increases *phase noise*.

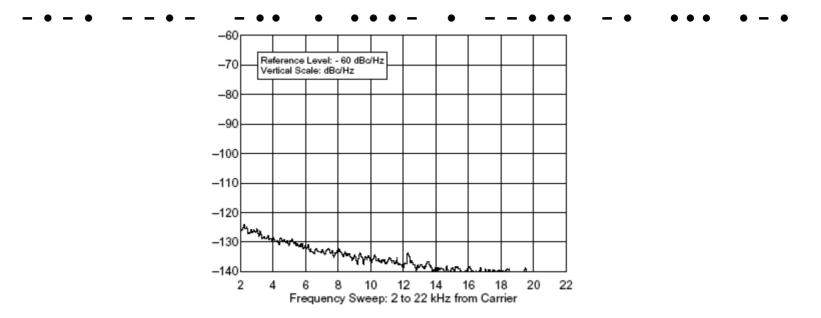

- **Phase noise:** noise produced by short-term, random phase jitter (fluctuations) in the VCO.

- Noise power increases with decreasing offset from carrier.

- Excessive phase noise mixes with RF signal at mixer input, degrading S/N at mixer output (reciprocal-mixing noise). This degrades dynamic range and selectivity.

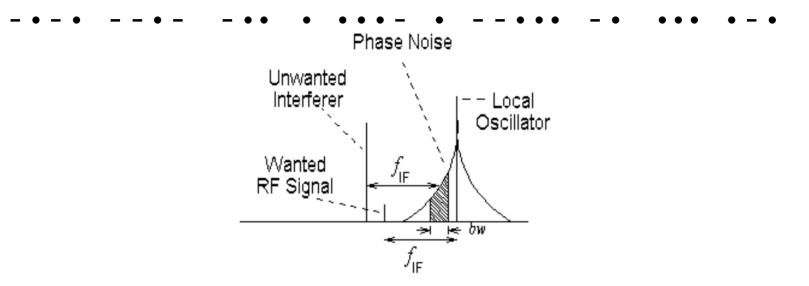

### **Reciprocal Mixing Noise**

Here the phase noise on the local oscillator is shown. To see the effect this can have on dynamic range and selectivity, imagine a strong interfering signal close to the wanted RF signal as shown. This unwanted signal can mix with the noise sidebands of the LO to also produce an output at the IF. This process is called reciprocal mixing. The noise sidebands involved are shown shaded in the figure.

Clock signal

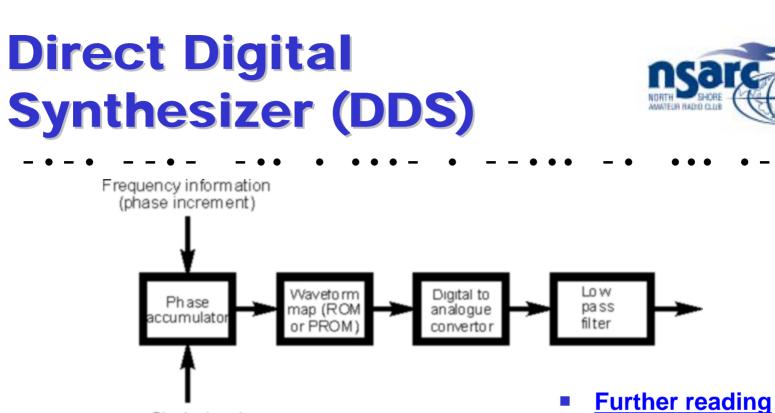

DDS operates by storing the points of a waveform in digital format, then recalling them to generate the waveform.

- Phase increment size, controlled by radio's CPU, determines rate at which DDS completes one cycle. This sets output frequency.

- Waveform map stores instantaneous amplitude vs. phase (point on cycle).

- DAC converts digital waveform amplitude values to analogue waveform.

- Low-pass filter integrates sinusoidal DAC output & attenuates harmonics.

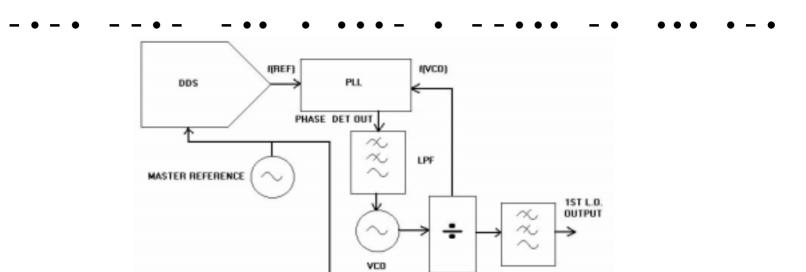

#### **DDS/PLL Synthesizer Example**

DDS supplies variable reference frequency to phase detector for comparison with divided VCO output.

**DIGITAL DIVIDERS**

LPE

2ND L.O. OUTPUT

- CPU sets output frequency by varying DDS freq. setting and divider ratio.

- Divider is optional, depending on VCO freq. range.

- Subsystem furnishes all local oscillators and carrier insertion ("BFO").

- Phase noise 10 to 30 dB lower than that achievable with classical PLL.

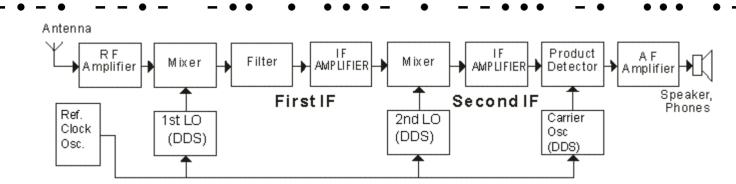

### **DDS HF Receiver**

Double-Conversion HF Receiver with DDS Local and Carrier Insertion Oscillators

- All oscillators are DDS's clocked from common master reference source (OCXO or TCXO).

- CPU "tunes" receiver by setting 1<sup>st</sup> LO freq.

- Receiver incremental tuning (RIT): CPU applies  $\Delta f$  to 1<sup>st</sup> LO.

- Passband tuning or IF shift: CPU varies 2<sup>nd</sup> LO freq.

- CPU shifts carrier osc. freq. for sideband selection.

## **Ancillary Receiver Functions**

- IF Shift (see HF Receivers 2, Slide 13)

- Passband Tuning (see HF Receivers 2, Slide 9)

- Tunable IF Notch Filter

- RIT & XIT Tuning

- RF Gain & Attenuator

- Split Operation in Transceiver

- Dual Watch

- Noise Blanker

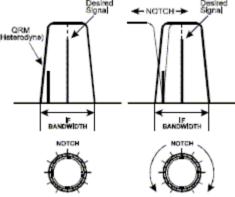

#### ← NOTCH→ Desired Signal Desired Sional QRM (Heterodyne BANDWIDT RANDWIDTH

#### **Tunable IF Notch** Filter

- **IF notch filter:** a narrow bandstop filter in the IF signal path.

- **NOTCH** control shifts notch-filter centre frequency within IF passband to notch out interfering carrier.

- As notch filter is inside AGC loop, interfering signal cannot swamp receiver.

- Notch filter attenuates interfering carrier by 50 dB (typical).

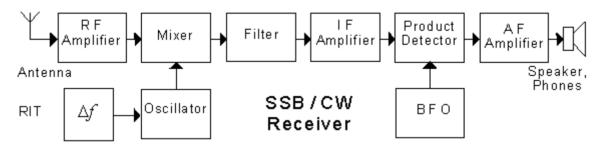

# **RIT & XIT Tuning**

- **RIT** (Receiver Incremental Tuning) applies a small  $\Delta f$  (± 10 kHz or less) to the local oscillator.

- Allows operator to tune in SSB, CW and RTTY signals accurately.

- RIT is also termed *Clarifier*.

- Modern transceivers also have XIT (Transmitter Incremental Tuning) similar function for transmitter.

- **RIT** and XIT  $\Delta f$  displayed separately from main freq. display.

- Pushbuttons allow addition of RIT/XIT offset to operating freq.

### **RF Gain & Attenuator**

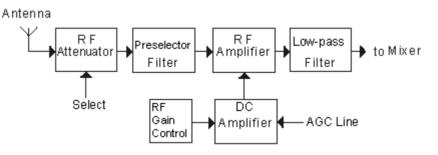

Gain-Controlled RF Amplifier with Front-End RF Attenuator

- **RF front-end attenuator** located between antenna input and preselector filter.

- 6, 12 or 18 dB attenuation (typical) selected by CPU.

- RF Gain control increases AGC bias on gain-controlled RF amplifier (or 1<sup>st</sup> IF amplifier in some designs); raises AGC threshold.

- Receiver dynamic range increases by amount of attenuation inserted.

- Usually, band noise is 10 to 12 dB above Rx noise floor; attenuation does not significantly degrade noise figure. Attenuator & RF Gain can be used together.

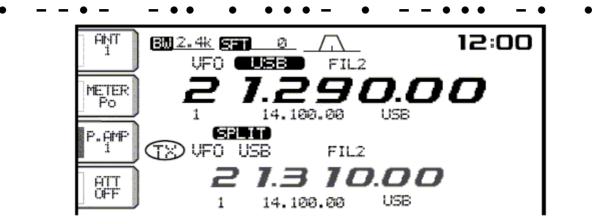

### **Split Operation in Transceiver**

- **Split operation:** receive on freq. A, transmit on freq. B.

- Easily implemented in modern transceivers; CPU stores and displays A and B frequencies separately as "VFO A" and "VFO B". Can select different modes and/or bands for A and B.

- Split enabled by pressing front-panel **SPLIT** key.

- In above example: Rx on 21.290 MHz; Tx on 21.310 MHz.

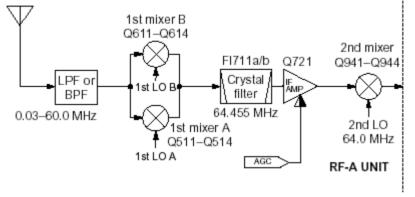

- Simplified dual-receive scheme developed by **Icom Inc.**

- Separate A & B 1<sup>st</sup> mixers and 1<sup>st</sup> LO's allow simultaneous reception of 2 signals.

- A & B 1<sup>st</sup> LO's are physically separate synthesizers.

- As RF and IF signal paths are shared, both signals must be in same mode and same (or adjacent) bands. Both signals are heard in audio output.

- Balance control adjusts relative gain of A & B channels.

- Dual watch can be combined with Split.

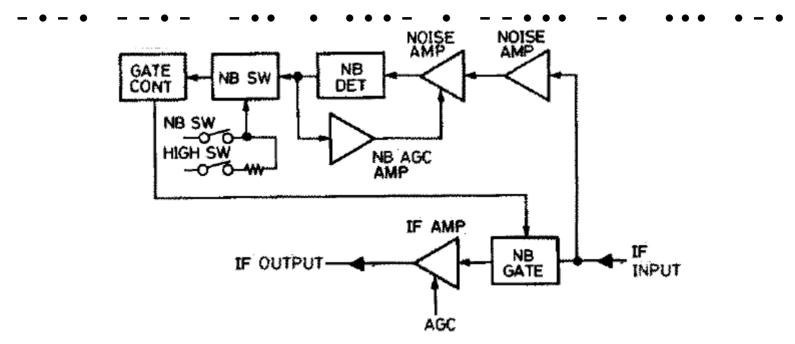

#### Noise Blanker (pulse-gate type)

- IF is typically 455 kHz. A portion of IF signal is amplified by NOISE AMP, detected by NB DET and applied to NB SW. HIGH SW switch increases NB SW threshold.

- When detected noise voltage exceeds NB SW threshold, NB SW sends transition to GATE CONT to close NB GATE & break IF signal path for duration of noise pulse.

- NB AGC loop time constant holds average signal level at NB DET constant, but is too long to respond to impulse noise.